FPGA时序约束学习笔记 |

您所在的位置:网站首页 › fpga slack为负 › FPGA时序约束学习笔记 |

FPGA时序约束学习笔记

|

一、基本操作

STEP1:quaturs ——> tool ——> TimeQuest Timing Analyzer

STEP2:Create Timing NetList(创建时序网表)

STEP3:读取SDC文件(设计约束文件)

STEP4:查看报告/创建时钟约束

(1)查看报告

report clocks

report top falling paths

report setup summary

report fmax summary

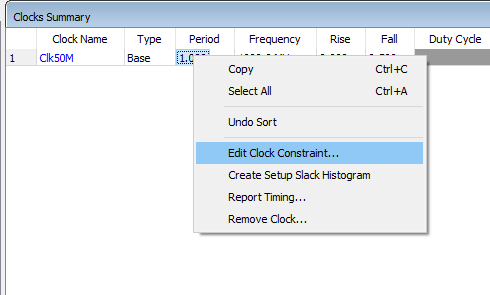

(2)创建时钟约束

1、constraints ——> creat clock

2、选中时钟

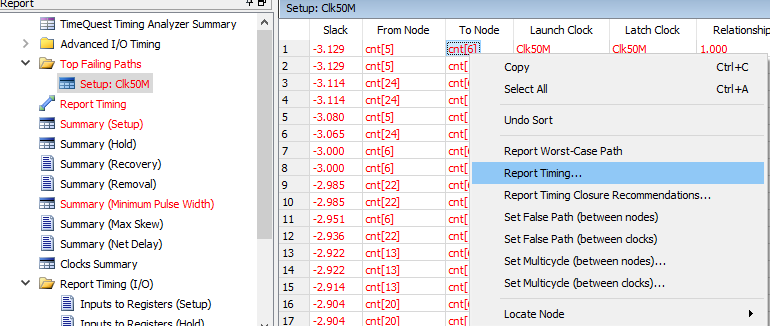

1、report top failing paths

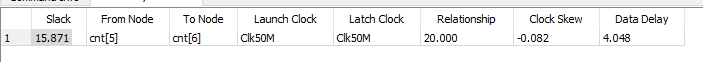

Slack:建立时间余量 From Node:源寄存器 To Node:目的寄存器 Lauch Clock:源寄存器时钟 Latch Clock:目的寄存器时钟 Relationship:源寄存器时钟与目的寄存器时钟差值 Clock Skew:时钟偏斜 Data Delay:数据延迟 2、时序分析建立在最极端的情况下,因此Slack要尽量最小(Slack >= 0时序才正确)

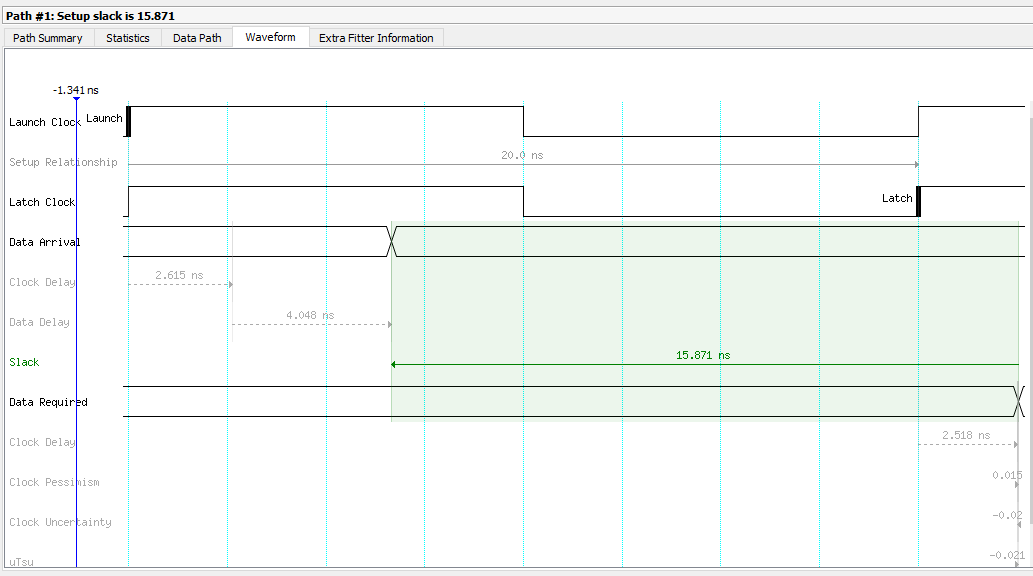

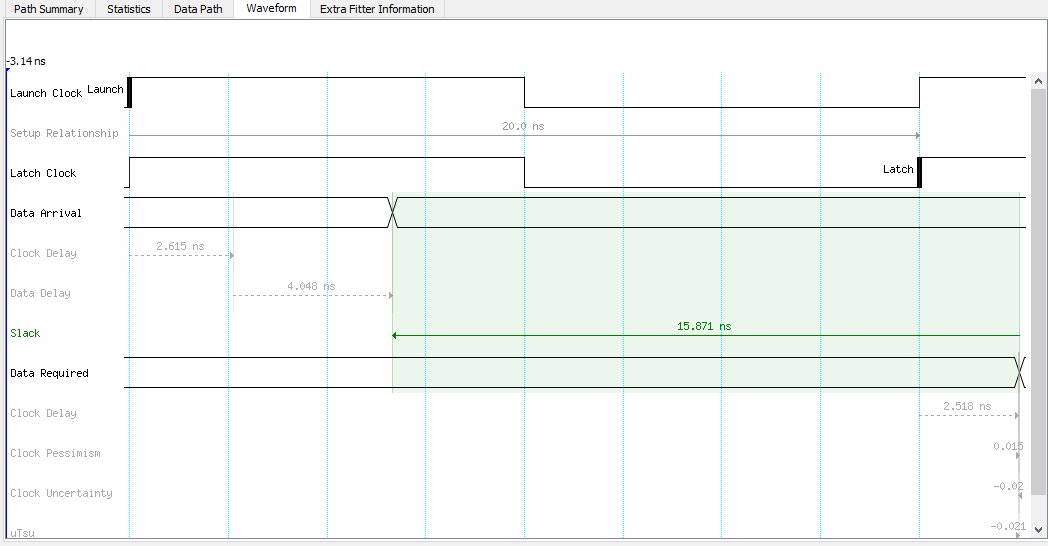

第一个clock delay:Tclk1

第二个clock delay:Tclk2

Tskew = Tclk2 - Tclk1

Slack = Tskew + ......

Slack取最小值,Skew就要取最小值,所以Tclk2取最小值,Tclk1取最大值

Clock Skew = Tskew + Clock Pessimism(悲观时钟)

Clock Pessimism(悲观时钟):时钟到达目的寄存器和源寄存器有共用的一段路,而Tclk1,Tclk2取的时钟速度不一样,因此共用的一段路需要补偿

Data Delay = Tco + Tdata (3)TsuTsu = uTsu + Clock Uncertainly TSu为负值:由于altera的FPGA芯片的特殊构造,Tsu可以取负值 Clock Uncertainly(不确定性时钟):时钟可能会有误差,例如:周期为20ns的时钟,有可能9.99999为低电平,10.00001高电平,时钟上升沿尽可能向左偏移,以至于建立时间向左偏移,才能使得Slack最小,所以Clock Uncertainly取负值 二、时序约束各参数意义(DataPath)

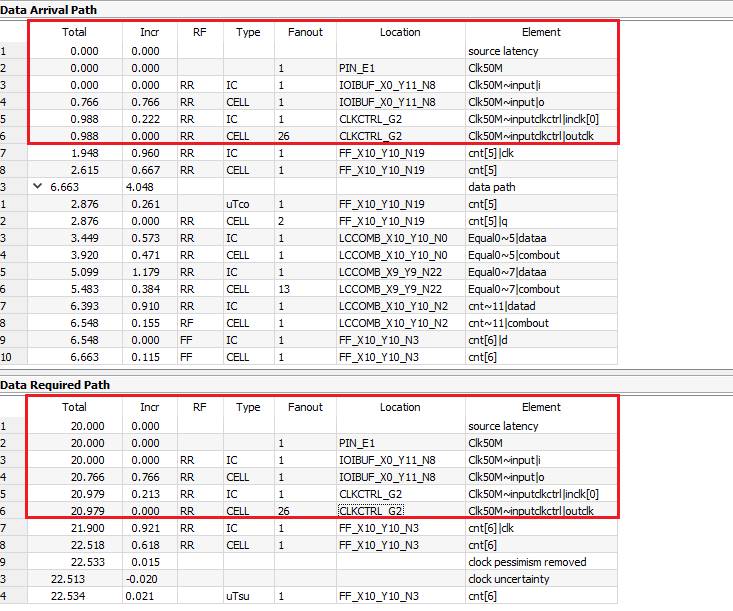

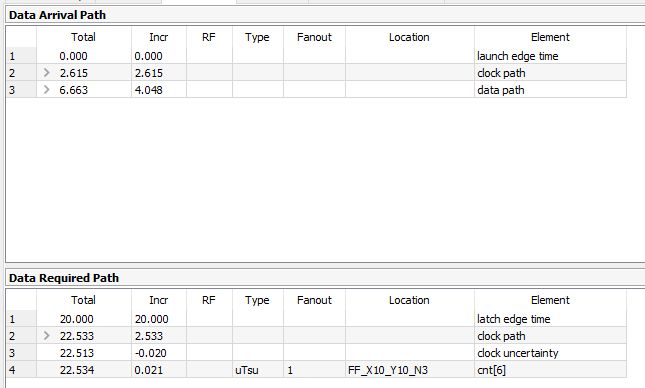

Data Arrival Path = Tclk1 + Tco + Tdata Clock Path = Tclk1 Data Path = Tdata + Tco (2) Data Required Path(数据要求时间)Data Required Path = Tclk + Tclk2 - Tsu |

【本文地址】

今日新闻 |

推荐新闻 |

write SDC File

faling的值可以去掉,自动生成占空比为50%的时钟

write SDC File

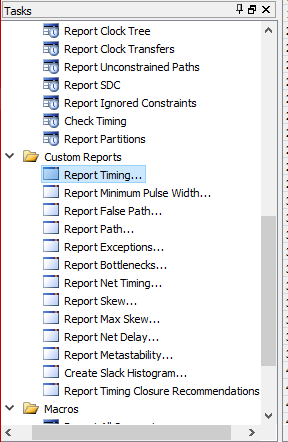

faling的值可以去掉,自动生成占空比为50%的时钟 2、report timing

2、report timing

Total:总时间

Incr:单步时间

Type:IC(内部走线时间),CELL(资源(寄存器)内部时间)

IBUF:缓冲器(三角符号)

CLKCTR:时钟树

Total:总时间

Incr:单步时间

Type:IC(内部走线时间),CELL(资源(寄存器)内部时间)

IBUF:缓冲器(三角符号)

CLKCTR:时钟树